US 20040263441A1

### (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2004/0263441 A1

Tanaka et al. (43) Pub. Date:

Dec. 30, 2004

#### (54) DISPLAY APPARATUS

(75) Inventors: Yukikazu Tanaka, Tokyo (JP); Tomoyuki Shirasaki, Tokyo (JP)

> Correspondence Address: FRISHAUF, HOLTZ, GOODMAN & CHICK, PC 767 THIRD AVENUE 25TH FLOOR NEW YORK, NY 10017-2023 (US)

(73) Assignee: Casio Computer Co., Ltd., Tokyo (JP)

(21) Appl. No.: 10/867,630

(22) Filed: Jun. 14, 2004

#### (30) Foreign Application Priority Data

Jun. 26, 2003 (JP) ...... 2003-182489

#### **Publication Classification**

| (51) | Int. Cl. <sup>7</sup> |        |

|------|-----------------------|--------|

| (52) | U.S. Cl.              | 345/76 |

#### (57) ABSTRACT

A display apparatus includes a substrate, a plurality of pixel electrodes which are arrayed on a side of one surface of the substrate, EL layers each of which is formed on a corresponding one of the pixel electrodes, and an counter electrode which is formed on the EL layers. An auxiliary electrode is electrically connected to the counter electrode and overlaps portions between the pixel electrodes.

FIG.1

FIG.2

FIG.5

FIG.6

FIG.7A

**IG.7B**

**FIG.16**

FIG. 17

**FIG.22**

**FIG.23**

**FIG.24**

**FIG.25**

#### **DISPLAY APPARATUS**

### CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is based upon and claims the benefit of priority from prior Japanese Patent Application No. 2003-182489, filed Jun. 26, 2003, the entire contents of which are incorporated herein by reference.

#### BACKGROUND OF THE INVENTION

[0002] 1. Field of the Invention

[0003] The present invention relates to a display apparatus having light-emitting elements arrayed on a substrate.

[0004] 2. Description of the Related Art

[0005] An electroluminescent element (to be abbreviated as an organic EL element) has a multilayered structure formed by forming a first electrode, an EL layer, and a second electrode on a glass substrate in this order. When a voltage is applied between the first electrode and the second electrode, holes and electrons are injected to the EL layer, and electroluminescence occurs in it. As described in Jpn. Pat. Appln. KOKAI Publication No. 6-151063, display light emitted by the EL layer emerges from the glass substrate on which the first electrode and the EL layer are formed in this order.

[0006] When a plurality of organic EL elements serving as pixels are arrayed in a matrix on a substrate, a display apparatus is provided. Such display apparatuses are roughly classified into two types: an active matrix driving system and a passive driving system (simple matrix driving system). In the active matrix driving display apparatus, the application voltage per unit time for an organic EL element is low. For this reason, the voltage applied on organic EL elements can be reduced, and the service life can be prolonged. The active matrix driving display apparatus is superior to the passive driving display apparatus in these characteristics.

[0007] In the active matrix driving display apparatus, a pixel transistor serving as a switching element is arranged in each pixel. The organic EL elements are selectively caused to emit light by the pixel transistors. In manufacturing an active matrix driving display apparatus, transistors are formed on a substrate before organic EL elements are formed in a matrix by patterning. This is because the temperature in transistor formation exceeds the heat-resistant temperature of organic EL elements.

[0008] In such a display apparatus, a transistor is formed for each pixel. In forming a plurality of organic EL elements in a matrix, first electrodes on the lower side, which are to be connected to transistors, are formed in a matrix independently for each organic EL element. On the other hand, a second electrode is formed on the entire surface of the display unit as a common electrode common to all the organic EL elements. The light-emitting region of each pixel of the display apparatus corresponds to a region where the first and second electrodes cross. In the active matrix driving display apparatus, the first electrodes can be patterned by photolithography. For this reason, pixels can be formed in a very high resolution as compared to a passive driving display apparatus because it requires second electrode patterning using a metal mask with a lower resolution than photolithography.

[0009] Light from the EL layer emerges through the glass substrate. In this case, the light incident on the glass substrate causes irregular reflection or is absorbed in the substrate because of its refractive index and thickness. Hence, a large quantity of light emitted from the EL layer is lost in the glass substrate. If the second electrode is transparent, the light from the EL layer can emerge through not the glass substrate but the second electrode. However, since a metal oxide used for a transparent electrode generally has a high electric resistance, a current hardly flows through it as compared to an opaque metal. If a single second electrode is formed as a common electrode for pixels, the light emission intensity in the plane becomes nonuniform, and more specifically, it is bright at a portion near a power supply but dark distantly from it. To obtain a sufficient sheet resistance, the second electrode must be thick. However, the transmittance becomes low in a thick second electrode.

#### BRIEF SUMMARY OF THE INVENTION

[0010] According to an aspect of the present invention, there is provided a display apparatus comprising: a substrate having one surface; a plurality of pixel electrodes which are arrayed on a side of the one surface of the substrate; EL layers each of which is formed on a corresponding one of the pixel electrodes; an counter electrode which is formed on the EL layers; and an auxiliary electrode which is electrically connected to the counter electrode and overlaps portions between the pixel electrodes.

[0011] In the display apparatus, the counter electrode may be transparent. The display apparatus has a structure which causes light from the EL layers to emerge through the counter electrode. Even when a material having a relatively high resistivity is used for the counter electrode, the auxiliary electrode is formed to be connected to the counter electrode and overlaps the portions between the plurality of pixel electrodes. For this reason, the total sheet resistance of the auxiliary electrode and counter electrode can be reduced without decreasing the light emergence ratio on a counter electrode surface. A variation in current density from the counter electrode to the EL layers can be improved. The current value of the current flowing through the counter electrode is almost constant, and light emission in the same pixel is uniformed. Since no strong electric field is applied to only part of the EL layer, the voltage applied on it can be reduced, and the service life can be prolonged. In the structure of a general EL panel, when the counter electrode is formed as a common electrode common to a larger number of pixels, and a metal oxide such as ITO is used to form a transparent electrode, the voltage value changes between a counter electrode portion near wiring lines which supply the voltage to the counter electrode and a counter electrode portion far apart from the wiring lines. That is, the voltage attenuates as the distance from the wiring lines increases, and the light emission luminance may be nonuniform in the plurality of pixels in the plane. This problem becomes more conspicuous as the area of the counter electrode increases. In the above present apparatus, however, since the auxiliary electrode may be formed in correspondence with the area level for each pixel, any variation in the applied voltage or the current value of the flowing current depending on the relative position between the wiring lines and each pixel can be suppressed. Even if signals of equipotential are output between all the pixels and the counter electrode, all the EL layers can emit light almost at the same intensity, and the light emission intensity in the plane can be uniformed.

[0012] In addition, since the counter electrode can be made thinner, the transmittance of the counter electrode to the light emitted by the EL layers can be increased. Furthermore, since the auxiliary electrode is arranged between the pixel electrodes, i.e., between the EL layer of a pixel electrode and the EL layer of an adjacent pixel electrode, the decrease in aperture ratio can be minimized.

[0013] When the counter electrode is transparent, and the auxiliary electrode has a light-shielding effect, light emitted by the EL layers emerges outside from the counter electrode. Generally, a transparent electrode material has a high resistivity. Hence, the decrease in sheet resistance by the auxiliary electrode is more effective. In addition, since the auxiliary electrode has the light-shielding effect, it functions as a light-shielding film between the pixel electrodes to prevent any decrease in contrast and color purity and any light leakage between the pixel electrodes (between the EL layers). Only the counter electrode is present as the layer between the EL layers and the auxiliary electrode. The auxiliary electrode is arranged close to the EL layers. For these reasons, even when the EL layers radially emit light, the prevention efficiency of the auxiliary electrode for decrease in contrast ratio and color purity and the light leakage is very high. Hence, the light can efficiently emerge outside from the counter electrode.

[0014] When a light-shielding mask overlapping the auxiliary electrode is formed on it, any decrease in contrast and color purity and any light leakage between the pixel electrodes (between the EL layers) can be prevented.

[0015] When the auxiliary electrode is formed into a mesh shape to overlap the entire region between the plurality of pixel electrodes, the voltage of the counter electrode can be more uniformed in the plane.

[0016] When the display apparatus further comprises an resonator which resonates at least some light components of light emitted by the EL layers, the emergence ratio of the wavelength range of a predetermined color of the light from the EL layers can be increased. Hence, the color purity can be increased.

[0017] The resonator may comprise a half-reflecting layer which is arranged under the pixel electrodes, a transparent layer which is formed under the half-reflecting layer while being in contact with the half-reflecting layer, and a reflecting layer which is formed under the transparent layer while being in contact with the transparent layer, a light transmittance increases in an order of the reflecting layer, the half-reflecting layer, and the transparent layer, a light reflectance increases in an order of the transparent layer, the half-reflecting layer, and the reflecting layer, and the pixel electrodes are transparent. In this case, of external light that enters the transparent layer, each component whose wavelength is not an integral multiple of ½ of the optical thickness of the transparent layer hardly emerges from the resonator even when the component causes interference while repeating reflection. Hence, the component is rarely reflected from the display apparatus. For this reason, glare caused by external light can be suppressed. Even when the display apparatus exists under a bright environment, any decrease in contrast ratio can be suppressed. Hence, a display apparatus of high visibility for a user can be provided.

[0018] The apparatus further comprises a transparent layer which is formed under the pixel electrodes while being in contact with the pixel electrodes, and a reflecting layer which is formed under the transparent layer while being in contact with the transparent layer, and in which a light transmittance increases in an order of the reflecting layer, the pixel electrodes, and the transparent layer, and a light reflectance increases in an order of the transparent layer, the pixel electrodes, and the reflecting layer. In this case, the pixel electrodes form part of the resonator. Hence, reflection of external light can be suppressed by a smaller number of components.

[0019] According to another aspect of the present invention, there is provided a display apparatus comprising a plurality of pixel electrodes which are arrayed on a side of one surface of a substrate; an auxiliary electrode which is provided around the pixel electrodes and is electrically connected to the pixel electrodes, is separated from the pixel electrodes; EL layers each of which is formed on a corresponding one of the pixel electrodes; and a counter electrode which is formed on the EL layers.

[0020] In the display apparatus according to this aspect, the sheet resistance can be reduced by combining the auxiliary electrode and pixel electrodes. For this reason, the EL layers can efficiently be caused to emit light at a low voltage. In addition, since the auxiliary electrode is arranged between the pixel electrodes, i.e., between the EL layer of a pixel electrode and the EL layer of an adjacent pixel electrode, the decrease in aperture ratio can be minimized.

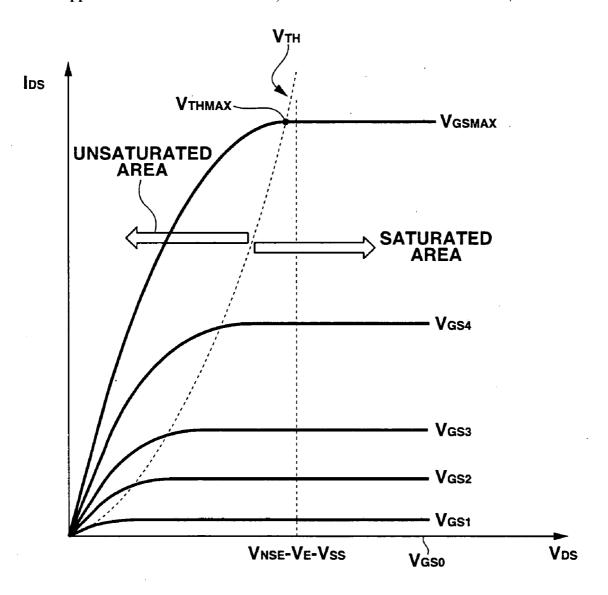

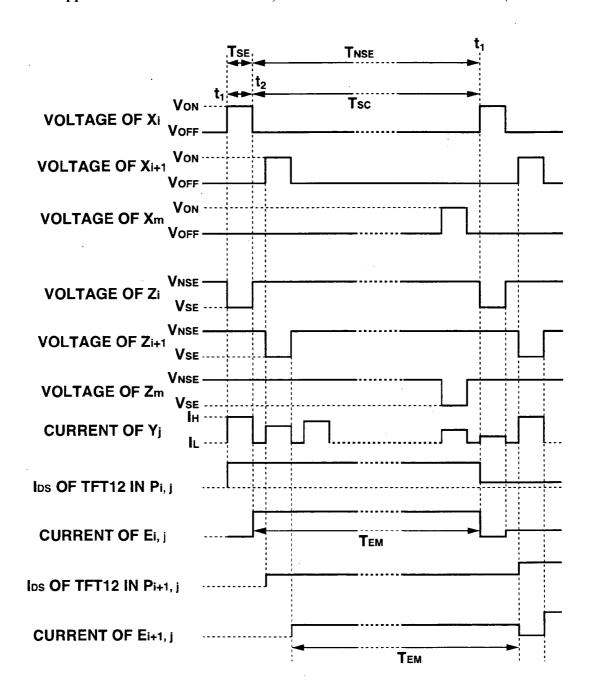

[0021] According to still another aspect of the present invention, there is provided a display apparatus comprising: a plurality of pixel electrodes which are arrayed on a side of one surface of a substrate; EL layers each of which is formed on a corresponding one of the pixel electrodes; a counter electrode which is formed on the EL layers; an auxiliary electrode which is electrically connected to the counter electrode and overlaps portions between the plurality of pixel electrodes; a plurality of current lines; a switch circuit which supplies a storage current having a predetermined current value to the current line during a selection period and stops supplying the current to the current line during a nonselection period; and a plurality of current storage circuits which store current data corresponding to the current value of the storage current which flows through the current line during the selection period and supply a display current having a current value substantially equal to the storage current to the EL layer through the pixel electrode during the nonselection period in accordance with the current data stored during the selection period.

[0022] Even when the display luminance is gray-level-controlled by the current value of a signal, like the storage current, the sheet resistance can be reduced by combining the auxiliary electrode and counter electrode. In addition, since the auxiliary electrode is arranged between the pixel electrodes, i.e., between the EL layer of a pixel electrode and the EL layer of an adjacent pixel electrode, the decrease in aperture ratio can be minimized.

## BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWING

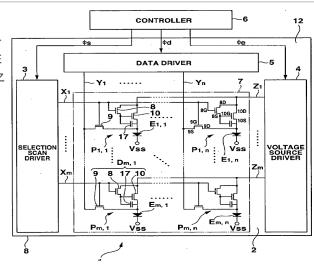

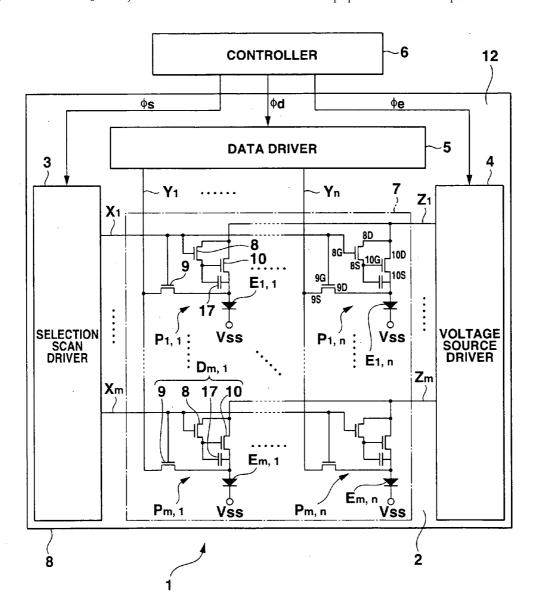

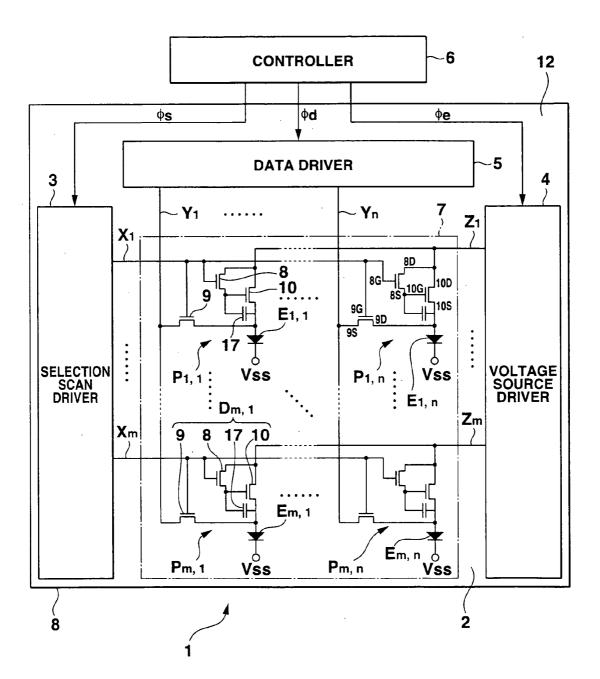

[0023] FIG. 1 is a plan view showing a display apparatus according to an embodiment of the present invention;

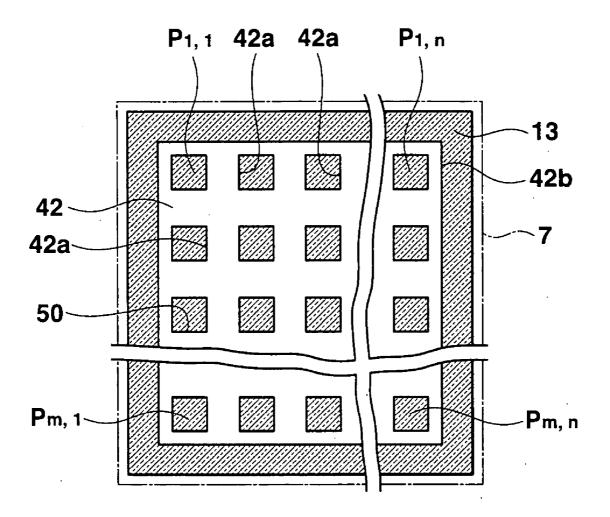

[0024] FIG. 2 is a plan view showing a counter transparent electrode and auxiliary electrode layer of organic EL elements in the display unit of the display apparatus shown in FIG. 1;

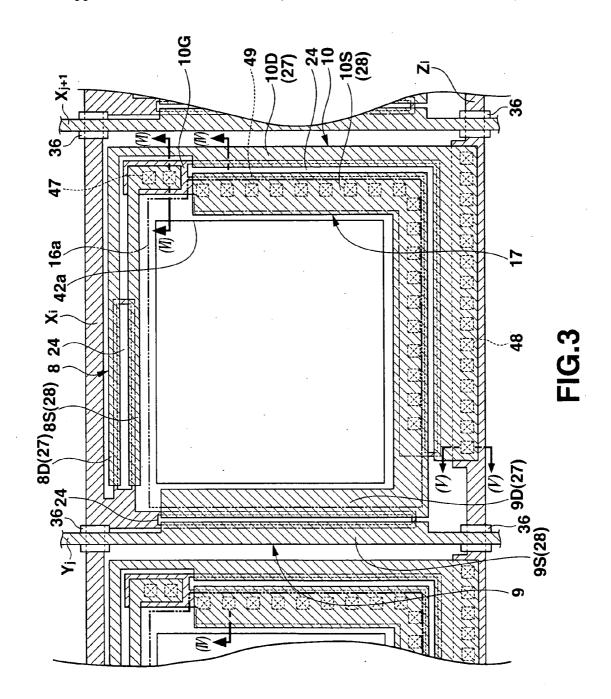

[0025] FIG. 3 is a plan view of a pixel driving circuit  $D_{i,j}$  in a pixel  $P_{i,j}$ ;

[0026] FIG. 4 is a sectional view taken along a line (IV)-(IV) in FIG. 3 in a direction of thickness;

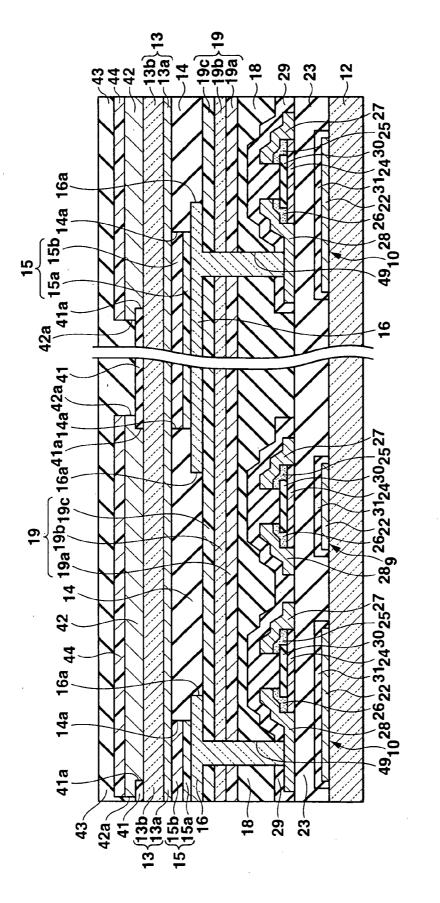

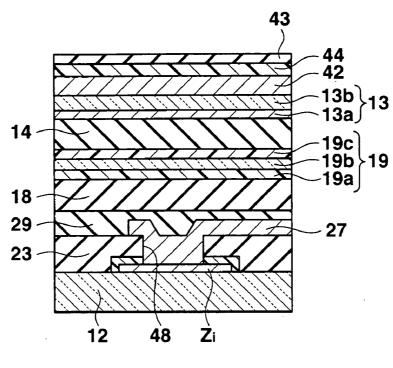

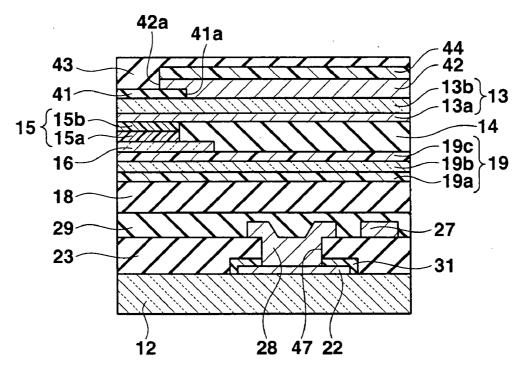

[0027] FIG. 5 is a sectional view taken along a line (V)-(V) in FIG. 3 in a direction of thickness;

[0028] FIG. 6 is a sectional view taken along a line (VI)-(VI) in FIG. 3 in a direction of thickness;

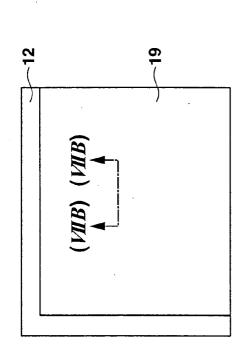

[0029] FIG. 7A is a view showing a step in manufacturing the display apparatus;

[0030] FIG. 7B is a sectional view taken along a line (VIIB)-(VIIB) in FIG. 7A;

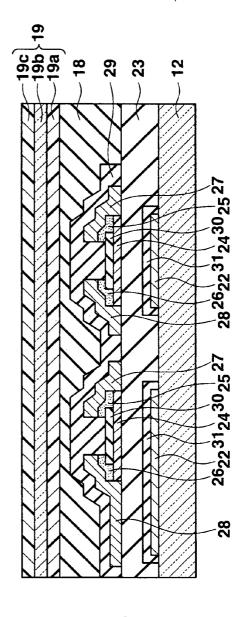

[0031] FIG. 8A is a view showing a step following FIG. 7A:

[0032] FIG. 8B is a sectional view taken along a line (VIIIB)-(VIIIB) in FIG. 8A;

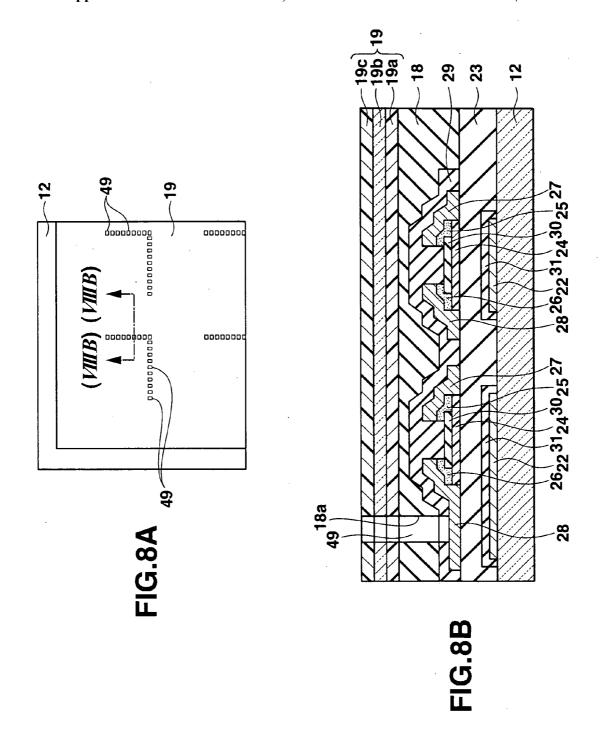

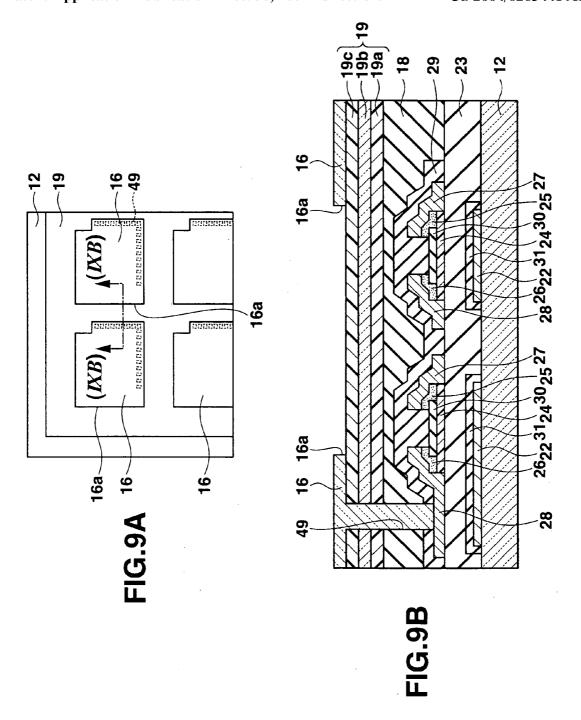

[0033] FIG. 9A is a view showing a step following FIG. 8A.

[0034] FIG. 9B is a sectional view taken along a line (IXB)-(IXB) in FIG. 9A;

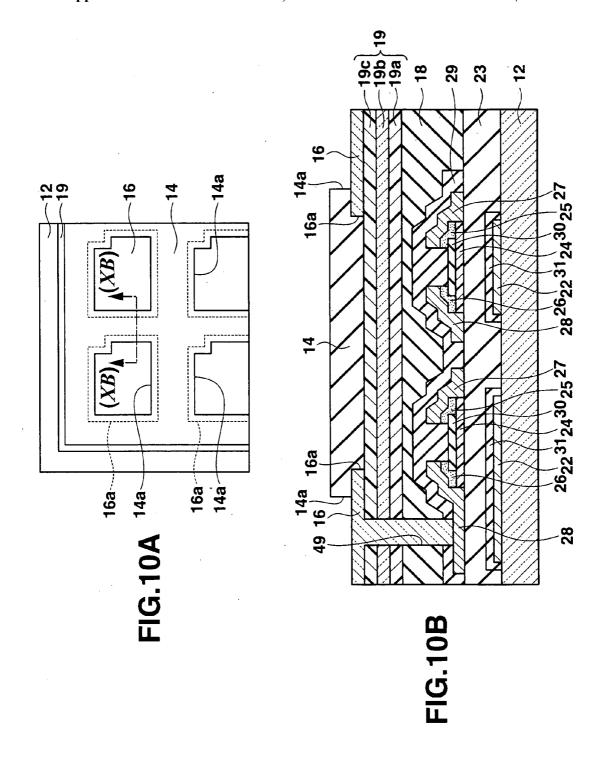

[0035] FIG. 10A is a view showing a step following FIG. 9A;

[0036] FIG. 10B is a sectional view taken along a line (X)-(X) in FIG. 10A;

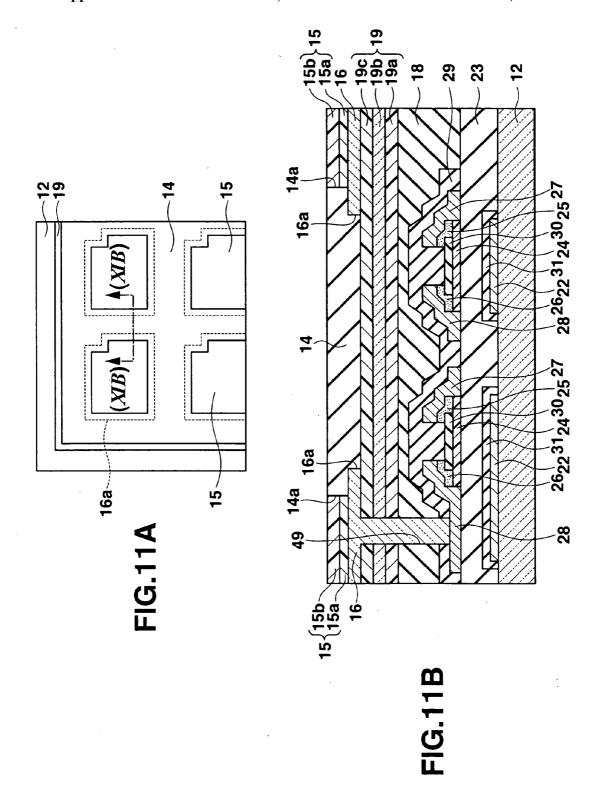

[0037] FIG. 11A is a view showing a step following FIG. 10A;

[0038] FIG. 11B is a sectional view taken along a line (XI)-(XI) in FIG. 11A;

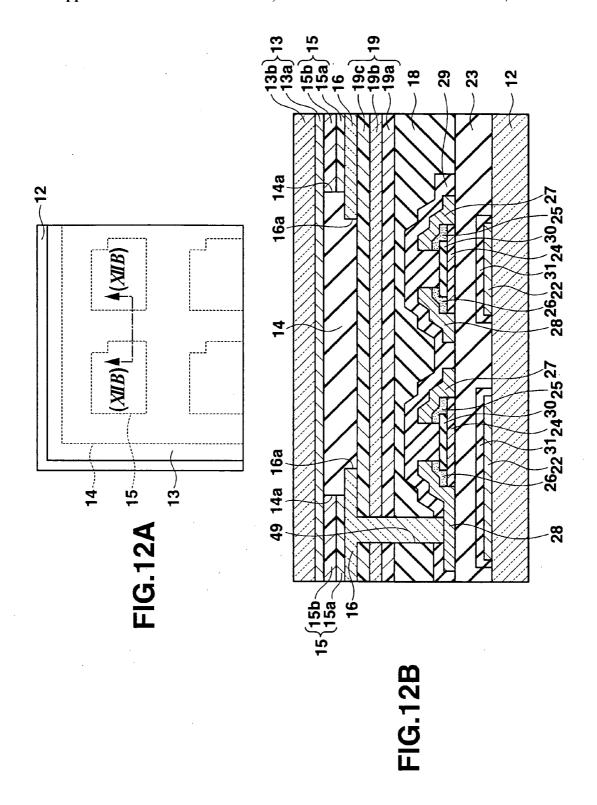

[0039] FIG. 12A is a view showing a step following FIG.

[0040] FIG. 12B is a sectional view taken along a line (XII)-(XII) in FIG. 12A;

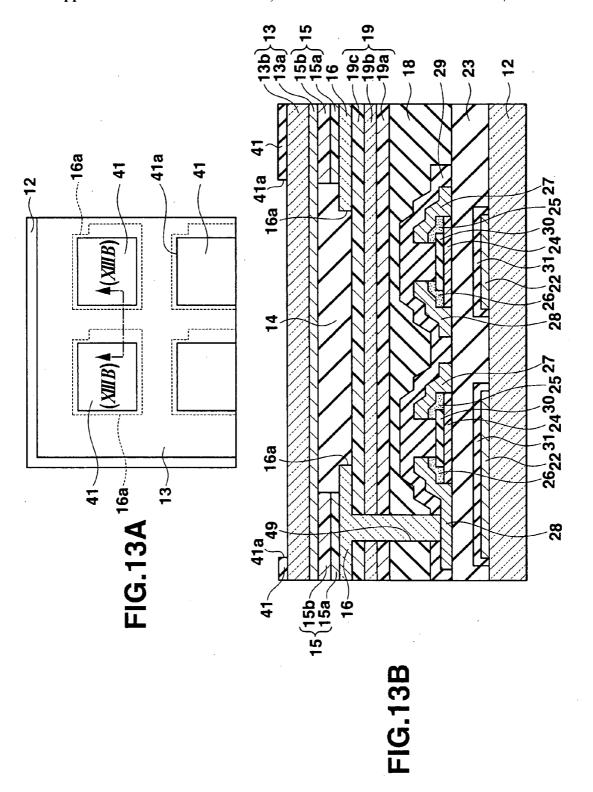

[0041] FIG. 13A is a view showing a step following FIG.

[0042] FIG. 13B is a sectional view taken along a line (XIIIB)-(XIIIB) in FIG. 13A;

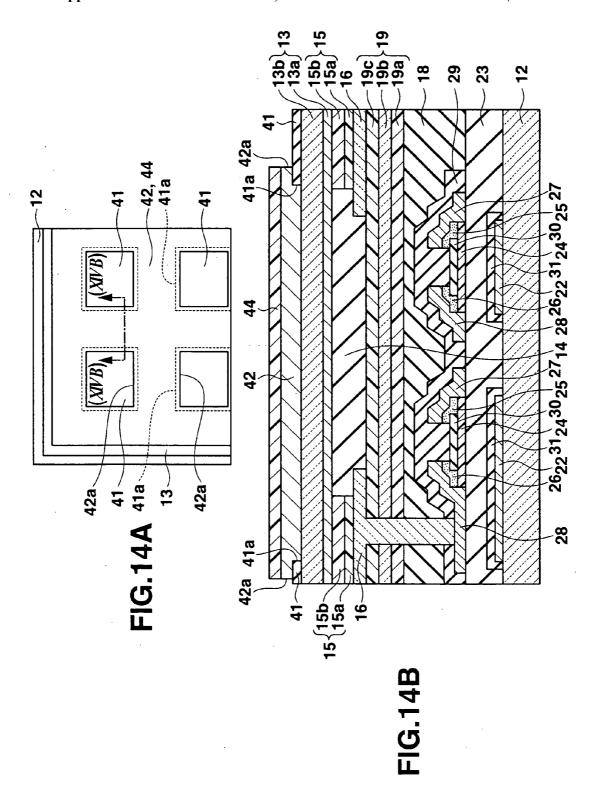

[0043] FIG. 14A is a view showing a step following FIG. 13A;

[0044] FIG. 14B is a sectional view taken along a line (XIVB)-(XIVB) in FIG. 14A;

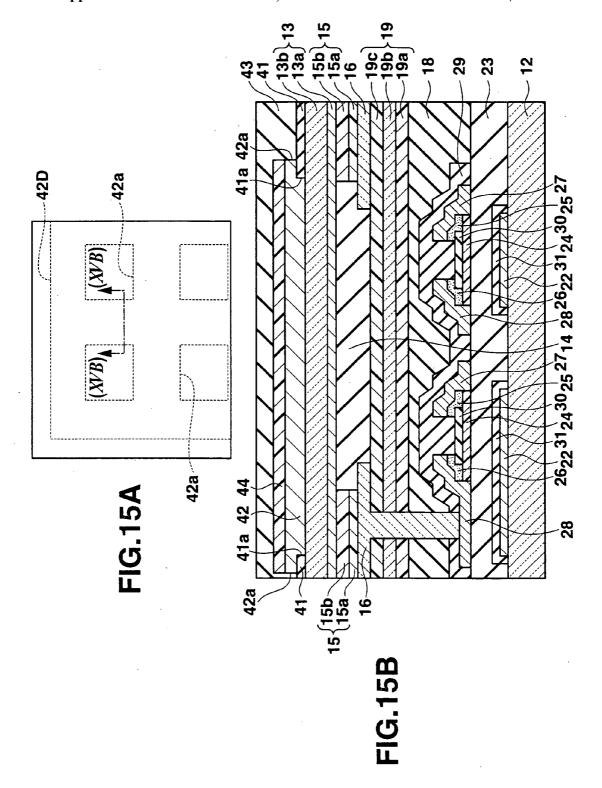

[0045] FIG. 15A is a view showing a step following FIG. 14A;

[0046] FIG. 15B is a sectional view taken along a line (XVB)-(XVB) in FIG. 15A;

[0047] FIG. 16 is a sectional view of another display apparatus to which the present invention is applied as the first modification and which is taken along the line (IV)-(IV) in FIG. 3 in a direction of thickness;

[0048] FIG. 17 is a sectional view of still another display apparatus to which the present invention is applied as the second modification and which is taken along the line (IV)-(IV) in FIG. 3 in a direction of thickness;

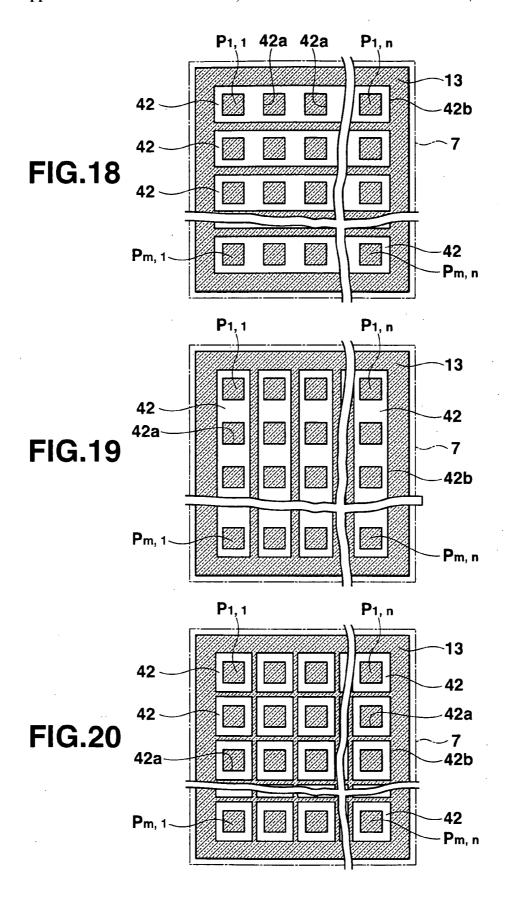

[0049] FIG. 18 is a plan view showing the counter transparent electrode and auxiliary electrode layer of organic EL elements in the display unit of still another display apparatus to which the present invention is applied as the third modification;

[0050] FIG. 19 is a plan view showing the counter transparent electrode and auxiliary electrode layer of organic EL elements in the display unit of still another display apparatus to which the present invention is applied as the fourth modification;

[0051] FIG. 20 is a plan view showing the counter transparent electrode and auxiliary electrode layer of organic EL elements in the display unit of still another display apparatus to which the present invention is applied as the fifth modification;

[0052] FIG. 21 is a sectional view of still another display apparatus to which the present invention is applied as the sixth modification and which is taken along the line (IV)-(IV) in FIG. 3 in a direction of thickness;

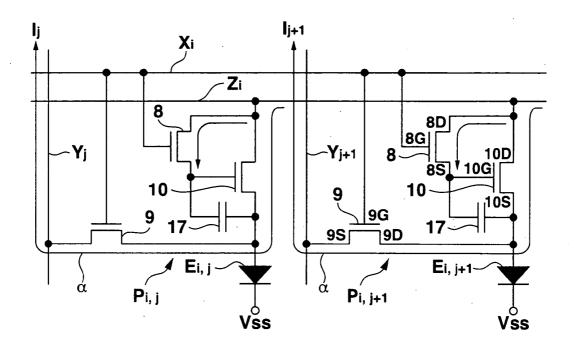

[0053] FIG. 22 is an equivalent circuit diagram of pixels in the display apparatus so as to explain the driving principle during the selection period;

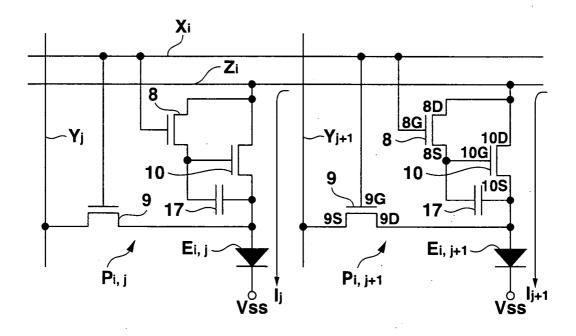

[0054] FIG. 23 is an equivalent circuit diagram of pixels in the display apparatus so as to explain the driving principle during the selection period;

[0055] FIG. 24 is a graph showing the relationship between a current which flows to an NMOSFET connected in series with a light-emitting element of the display apparatus and a voltage applied to the NMOSFET; and

[0056] FIG. 25 is a timing chart showing the operation of a driving circuit.

## DETAILED DESCRIPTION OF THE INVENTION

[0057] Detailed embodiments of the present invention will be described below with reference to the accompanying drawings. However, the scope of the present invention is not limited to the illustrated examples. In the following description, "viewed from the upper side" means "viewed perpendicularly to the display surface".

[0058] FIG. 1 is a block diagram schematically showing an entire arrangement of a display apparatus to which the present invention is applied. As shown in FIG. 1, the display apparatus 1 is a so-called active matrix driving display apparatus which comprises, as the basic arrangement, an active matrix display panel 2 and a controller 6 which controls the entire light-emitting display 1. The display panel 2 includes a substrate 12 (FIG. 4) made of borosilicate glass, silica glass, or glass of another type, which has a resistance to the temperature during a transistor manufacturing process (to be described later), a display unit 7 which

is formed on the substrate 12, as a plurality of pixels, and emits light to display an image corresponding to image data from the controller 6, and a selection scan driver 3, voltage source driver 4 and data driver 5, which are formed on the substrate 12 to drive the pixels of the display unit 7. The selection scan driver 3, voltage source driver 4, and data driver 5 are connected to be able to receive data and control signals \$\phi\$, \$\phi\$e, and \$\phi\$d from the controller 6, respectively. The display panel 2 is formed by arranging various kinds of wiring lines and elements on the substrate 12. The substrate 12 need not always have a high transmittance for visible light.

[0059] In the display panel 2,  $\underline{m}$  selection scan lines  $X_1, X_2, \ldots, X_m$  are formed on the substrate 12 while being arrayed parallel to each other along the row direction. In addition,  $\underline{m}$  voltage source scan lines  $Z_1, Z_2, \ldots, Z_m$  are formed on the substrate 12 along the row direction. The voltage source scan lines  $Z_1, Z_2, \ldots, Z_m$  and the selection scan lines  $X_1, X_2, \ldots, X_m$  are alternately arranged to form pairs. The voltage source scan lines  $Z_1, Z_2, \ldots, Z_m$  are electrically insulated from the selection scan lines  $X_1, X_2, \ldots, X_m$ . Current lines  $Y_1, Y_2, \ldots, Y_n$  are formed on the substrate 12 along the column direction perpendicular to the row direction. The selection scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $Z_1, Z_2, \ldots, Z_m$  can be formed at once by patterning a single conductive film. The current lines  $Y_1, Y_2, \ldots, Y_n$  cross the selection scan lines  $X_1, X_2, \ldots, X_m$ . The selection scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $Z_1, Z_2, \ldots, Z_m$ . The selection scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $Z_1, Z_2, \ldots, Z_m$ . The selection scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $Z_1, Z_2, \ldots, Z_m$ . The selection scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $Z_1, Z_2, \ldots, Z_m$ . The selection scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $X_1, X_2, \ldots, X_m$  and volt

[0060] A plurality of organic EL elements are arrayed in a matrix on the substrate 12. Each organic EL element is formed in each region surrounded by adjacent two of the current lines  $Y, Y_2, \ldots, Y_n$  and adjacent two of the selection scan lines  $X_1, X_2, \ldots, X_m$ . A driving circuit to supply a predetermined current to the organic EL element is formed about that organic EL element. One organic EL element and a driving circuit arranged for it correspond to one pixel of the display panel 2. That is, one organic EL element is formed for each of  $(m \times n)$  pixels.

[0061] The display panel 2 will be described below in detail.

[0062] A plurality of pixels  $P_{1,1}$  to  $P_{m,n}$  ( $m \ge 1$ , and  $n \ge 2$ ) are formed in a matrix in the display unit 7 in the display panel 2. In a pixel  $P_{i,j}$  ( $1 \le i \le m$ , and  $1 \le j \le n$ ) of the ith row and jth column, an organic EL element  $E_{i,j}$  of the ith row and jth column and a pixel driving circuit  $D_{i,j}$  of the ith row and jth column, which drives the organic EL element  $E_{i,j}$ , are formed. The pixel driving circuit  $D_{i,j}$  comprises a capacitor 17, first transistor 8, second transistor 9, and third transistor 10. The transistors are n-channel amorphous silicon thinfilm transistors.

[0063] A gate electrode 8G of the first transistor 8 of the pixel driving circuit  $D_{i,j}$  is connected to a selection scan line  $X_i$  of the ith row. A drain electrode 8D is connected to a voltage source scan line  $Z_i$  of the ith row. A source electrode 8S is connected to a gate electrode 10G of the third transistor 10 and one electrode of the capacitor 17.

[0064] A gate electrode 9G of the second transistor 9 of the pixel driving circuit  $D_{i,j}$  is connected to the selection scan

line  $X_i$  of the ith row. A drain electrode 9D is connected to a source electrode 10S of the third transistor 10 and the other electrode of the capacitor 17. A source electrode 9S is connected to a current line  $Y_i$  of the jth column.

[0065] The gate electrode 10G of the third transistor 10 of the pixel driving circuit  $D_{i,j}$  is connected to the source electrode 8S of the first transistor 8 and one electrode of the capacitor 17, as mentioned above. A drain electrode 10D is connected to the voltage source scan line  $Z_i$ . The source electrode 10S is connected to a pixel electrode as one electrode of the organic EL element  $E_{i,j}$ , the other electrode of the capacitor 17, and the drain electrode 9D of the second transistor 9.

[0066] The capacitor 17 is connected between the gate electrode 10G and the source electrode 10S of the third transistor 10. The capacitor 17 has a function of holding the potential between the gate electrode 10G and the source electrode 10S.

[0067] The organic EL element  $E_{i,j}$  has a structure in which an organic EL layer 15 is sandwiched between a pixel electrode 16 and a counter electrode 13, as shown in FIG. 6. The pixel electrode is connected to the source electrode 10S of the third transistor 10. A reference potential  $V_{\rm SS}$  is applied to the counter electrode 13.

$[0068]\,$  In the display unit 7, as shown in FIG. 2, the counter transparent electrode 13 serving as the common electrode of organic EL elements  $E_{1,1}$  to  $E_{m,n}$  is formed all over the plurality of pixels  $P_{1,1}$  to  $P_{m,n}$ . An auxiliary electrode layer 42 is formed in contact with the counter transparent electrode 13. The auxiliary electrode layer 42 is made of a conductive material whose resistivity is lower than a transparent conductive layer 13b (FIGS. 5 and 6) of the counter transparent electrode 13. The auxiliary electrode layer 42 has a function of reducing the sheet resistance of the electrode including both itself and the counter transparent electrode 13. Since this conductive material is opaque to visible light, the auxiliary electrode layer 42 has opening portions 42a corresponding to the pixels. The organic EL layer 15 (to be described later), and the pixel electrode 16 and the counter transparent electrode 13, which are located on both surfaces of the organic EL layer 15, are exposed to the region in each opening portion 42a. Hence, the auxiliary electrode layer 42 covers the selection scan lines  $X_1$  to  $X_{\rm m}$ , current lines  $Y_1$  to  $Y_n$ , and voltage source scan lines  $Z_1$  to  $Z_m$ around the organic  $\bar{EL}$  elements  $E_{1,1}$  to  $E_{m,n}$ . In addition, to prevent glare caused by external light reflection on the source and drain electrodes of the first transistors 8, second transistors 9, and third transistors 10 of pixel driving circuits D<sub>1,1</sub> to D<sub>m,n</sub>, the auxiliary electrode layer 42 preferably covers the first transistors 8, second transistors 9, and third transistors 10 of the pixel driving circuits  $D_{i,j}$ . If external light reflection occurs even on the capacitor 17, it is also preferably covered with the auxiliary electrode layer 42.

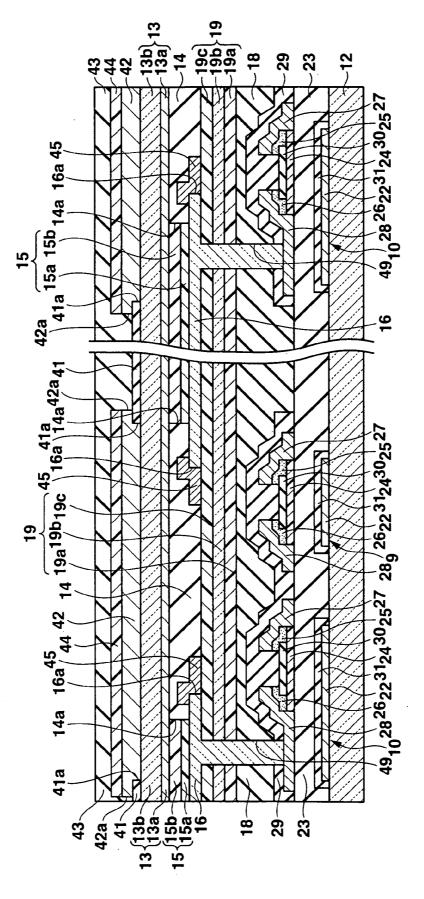

[0069] The pixel  $P_{i,j}$  will be described here in detail. FIG. 3 is a schematic view showing the pixel driving circuit  $D_{i,j}$  in the pixel  $P_{i,j}$  viewed from the upper side. FIG. 4 is a sectional view taken along a line (IV)-(IV) in FIG. 3 in a direction of thickness. FIG. 5 is a sectional view taken along a line (V)-(V) in FIG. 3 in a direction of thickness. FIG. 6 is a sectional view taken along a line (VI)-(VI) in FIG. 3 in a direction of thickness. To help understanding, the gate insulating film 23 (to be described later), a first impurity-

doped semiconductor film 25, a second impurity-doped semiconductor film 26, a block insulating film 36, and the counter transparent electrode 13 are not at least partially illustrated in FIG. 3.

[0070] A gate electrode layer 22 having a predetermined pattern, which serves as the gate electrode 8G of the first transistor 8, the gate electrode 9G of the second transistor 9, and the gate electrode 10G of the third transistor 10, is formed on the substrate 12. The gate electrode layer 22 is formed by patterning the same conductive material layer as the selection scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $Z_1, Z_2, \ldots, Z_m$  at once. The gate electrode layer 22 has a low-resistant material such as chromium, aluminum, copper, titanium, or tungsten or an alloy selected from at least some of them.

[0071] An anodic oxide film 31 is formed on the gate electrode layer 22 by anodizing its peripheral surface. The gate insulating film 23 is formed to cover the entire surface of the display unit 7. The gate insulating film 23 is made of a translucent and insulating material such as silicon nitride or silicon oxide. The gate insulating film 23 covers even the selection scan lines  $X_1, X_2, \ldots, X_m$  and voltage source scan lines  $Z_1, Z_2, \ldots, Z_m$ .

[0072] The semiconductor films 24 of the first transistor 8, second transistor 9, and third transistor 10 are formed to oppose the gate electrode layers 22 through parts of the gate insulating film 23. The semiconductor film 24 is made of intrinsic amorphous silicon having a spectral sensitivity from visible light to the infrared wavelength range. A blocking insulating film 30 made of silicon nitride is formed on each semiconductor film 24 to protect its surface from an etchant. The first impurity-doped semiconductor film 25 and second impurity-doped semiconductor film 26 separated from each other are formed on both and portions of each semiconductor film 24 and each blocking insulating film 30. The second impurity-doped semiconductor film 26 thus covers one side of the semiconductor film 24 and one side of the blocking insulating film 30. The second impuritydoped semiconductor film 26 also covers the other side of the semiconductor film 24 and the other side of the blocking insulating film 30. The first impurity-doped semiconductor film 25 and second impurity-doped semiconductor film 26 are made of amorphous silicon doped with n-type impurity ions.

[0073] A drain electrode layer 27 serving as the drain electrodes 8D, 9D, and 10D is formed on the first impuritydoped semiconductor films 25 of the first transistor 8, second transistor 9, and third transistor 10. A source electrode layer 28 serving as the source electrodes 8S, 9S, and 10S is formed on the second impurity-doped semiconductor films 26 of the first transistor 8, second transistor 9, and third transistor 10. The drain electrode layer 27 and source electrode layer 28 are formed by patterning the same conductive material layer as the current lines  $Y_1$  to  $Y_n$  at once. The drain electrode layer 27 and source electrode layer 28 are made of a low-resistant material such as chromium, aluminum, copper, titanium, or tungsten or an alloy selected from at least some of them and have a function of shielding visible light. With this structure, any external light or light from each organic EL element is suppressed from becoming incident on the semiconductor film 24, first impurity-doped semiconductor film 25, and second impurity-doped semiconductor film 26. The source electrode layer 28 and drain electrode layer 27 are separated and accordingly electrically insulated from each other.

[0074] The first transistor 8, second transistor 9, and third transistor 10 may have not the inverted staggered structure but a coplanar structure. At least some of them may be p-channel transistors. The transistors may be made of not amorphous silicon but, e.g., polysilicon. To prevent photodeterioration of the first transistor 8, second transistor 9, and third transistor 10, the substrate 12 may have a light-shielding effect.

[0075] A protective insulating film 29 made of silicon nitride is formed to cover the first transistor 8, second transistor 9, third transistor 10, capacitor 17, selection scan lines  $X_1, X_2, \ldots, X_m$ , current lines  $Y_1, Y_2, \ldots, Y_n$ , and voltage source scan lines  $Z_1, Z_2$ .

[0076] The third transistor 10 having the above structure is an MOSFET having the semiconductor film 24 as a channel region. The first transistor 8 and second transistor 9 have almost the same structure as the above-described third transistor 10. One electrode of the capacitor 17 is also used as the gate electrode layer 22 of the third transistor 10. The other electrode of the capacitor is also used as the source electrode layer 28 of the third transistor 10. The capacitor 17 uses the gate insulating film 23 formed between one electrode and the other electrode as a dielectric. Accordingly, the capacitor 17 functions as a capacitor which stores, as charge data, the gate-to-source potential of the third transistor 10 corresponding to the value of a current flowing between the source and the drain of the third transistor 10. That is, the capacitor 17 stores charge data written as the parasitic capacitance between the gate and the source of the third transistor 10. The capacitor 17 holds the charges stored between the gate and the source of the third transistor 10 so as to supply a current having the same value as in the write between the source and the drain of the third transistor 10 when a predetermined voltage is applied between the source and the drain of the third transistor 10.

[0077]  $\,\,$  The protective insulating film 29 is covered with an insulating planarization film 18 made of, e.g., polyimide. The insulating planarization film 18 functions as a planarization film formed over the entire surface of the substrate 12. Steps generated between the parts of the protective insulating film 29 on the first transistor 8, second transistor 9, and third transistor 10 and a part of the protective insulating film 29 on the surface of the substrate 12 are canceled by the insulating planarization film 18. Hence, the insulating planarization film 18 has an almost flat upper surface. The insulating planarization film 18 is made of a resin (e.g., methacrylate resin, acrylic resin, or epoxy resin). To prevent photo-deterioration of the first transistor 8, second transistor 9, and third transistor 10, the insulating planarization film 18 may have a light-shielding effect by containing a pigment such as carbon black.

[0078] An optical interference layer 19 is formed on the insulating planarization film 18 in correspondence with the entire surface of the display unit 7. The optical interference layer 19 is formed by forming, sequentially from the side of the insulating planarization film 18, a reflecting layer 19a which reflects light from the upper side by specular reflection, an optically transparent layer 19b which is set to a predetermined thickness and predetermined refractive

index, and a half-reflecting layer 19c which functions as a half-mirror. The optical interference layer 19 is optically designed such that the reflectance to light in the visible light wavelength range increases in the order of transparent layer 19b, half-reflecting layer 19c, and reflecting layer 19a, and the transmittance to light in the visible light wavelength range increases in the order of reflecting layer 19a, halfreflecting layer 19c, and transparent layer 19b. The reflecting layer 19a is a film made of a metal such as Ag, Pt, Cu, or Sn or an alloy thereof and having a smooth upper surface with a metallic luster. The transparent layer 19b is made of a dielectric such as silicon oxide or titanium oxide. The transparent layer 19b can have a single-layered structure but preferably has a multilayered structure. To make the optical interference layer 19 have an optical thickness corresponding to the light emission wavelength of each organic EL element which emits light of red, green, or blue (to be described later), optical interference layers may be arrayed in a plurality of independent matrices for each pixel or a pixel group of each color when viewed from the upper side. The optical interference layer 19 may have a single-layered

[0079] The drain electrode layer 27 of each third transistor 10 is connected to one of the voltage source scan lines  $Z_1$ ,  $Z_2$ , ...,  $Z_m$  through a contact hole 48 formed in the gate insulating film 23 and anodic oxide film 31.

[0080] The source electrode layer 28 of each first transistor 8 and the gate electrode layer 22 of a corresponding one of the third transistors 10 are connected through a contact hole 47 formed in the gate insulating film 23 and anodic oxide film 31.

[0081] The organic EL elements  $E_{1,1}$  to  $E_{m,n}$  are formed on the optical interference layer 19. Each of the organic EL elements  $E_{1,1}$  to  $E_{m,n}$  has a multilayered structure in which the pixel electrode 16 functioning as, e.g., an anode electrode, the EL layer 15 which causes electroluminescence when a current equal to or more than a threshold value flows, and the counter transparent electrode 13 functioning as, e.g., a cathode electrode are formed in this order.

[0082] The pixel electrode 16 is connected to the source electrode layer 28 of the third transistor 10 through a contact hole 49 formed in the insulating planarization film 18, optical interference layer 19, and protective insulating film 29.

[0083] The pixel electrodes 16 are independently formed while being separated from each other to electrically separate the pixels. A plurality of pixel electrodes 16 are arrayed in a matrix when viewed from the upper side.

[0084] On a portion of the optical interference layer 19 around the pixel electrode 16, a liquid-repellent film 14 which repels a liquid is formed while overlapping part of an edge portion 16a of the pixel electrode 16. The liquid-repellent film 14 has an opening portion 14a at a position corresponding to the central portion of the pixel electrode 16. The EL layer 15 is deposited in the opening portion 14a. The EL layer 15 is made of a light-emitting material. The EL layer 15 emits light by recombining carriers (holes) injected from the pixel electrode 16 and carriers (electrons) injected from the counter transparent electrode 13. The EL layer 15 of each of the organic EL elements  $E_{1,1}$  to  $E_{m,n}$  of the pixels  $P_{1,1}$  to  $P_{m,n}$  emits light of red, green, or blue. The EL layers

15 are arrayed such that the colors are periodically arranged. The EL layers 15 which emit light of the same color may be arrayed in the same column. Alternatively, the red, green, and blue EL layers 15 may be arrayed in a delta array.

[0085] The pixel electrode 16 is conductive and transparent to visible light. As long as it functions as an anode, the work function is preferably relatively high. The pixel electrode 16 is made of, e.g., indium oxide, zinc oxide, or tin oxide, or a mixture containing at least one of them (e.g., indium tin oxide (ITO), indium zinc oxide, or cadmium tin oxide (CTO)). When the pixel electrode 16 is formed as a half mirror, the half-reflecting layer 19c can be omitted. In this case, the reflectance to light in the visible light wavelength range increases in the order of transparent layer 19b, pixel electrode 16, and reflecting layer 19a, and the transmittance to light in the visible light wavelength range increases in the order of reflecting layer 19a, pixel electrode 16, and transparent layer 19b. Even in this case, the optical thickness of the transparent layer 19b is an integral multiple of ½ of the dominant wavelength (peak wavelength) of light emitted from the EL layer 15 of the organic EL element. When the optical interference layer 19 is omitted, the pixel electrode 16 need not always be transparent. The pixel electrode 16 preferably has reflective to light in the visible light wavelength range.

[0086] The EL layer 15 may appropriately contain either an electron transport substance that transports electrons by an electric field or a hole transport substance that transports holes by an electric field, or both an electron transport substance and a hole transport substance. More specifically, the EL layer 15 may have a three-layered structure including a hole transport layer, a light-emitting layer, and an electron transport layer sequentially formed from the pixel electrode 16. The EL layer 15 may have a two-layered structure sequentially including a hole transport layer and a lightemitting layer or a two-layered structure sequentially including a light-emitting layer and an electron transport layer. The EL layer 15 may have a single-layered structure including a light-emitting layer. Alternatively, the EL layer 15 may have a multilayered structure in which an electron or hole injection layer is inserted between appropriate layers in one of the above layer structures. All the layers included in the EL layer 15 may be made of organic compounds. Alternately, all the layers included in the EL layer 15 may be made of inorganic compounds. The EL layer 15 may be formed by stacking a layer made of an inorganic compound and a layer made of an organic compound. When all the layers included in the EL layer 15 are made of inorganic compounds, an inorganic EL element is formed in place of an organic EL element. When the EL layer 15 includes a layer of an organic compound, an organic EL element is formed.

[0087] When the EL layer 15 is made of a low molecular weight organic material or an inorganic substance, the EL layer 15 can be formed by epitaxial growth such as deposition or sputtering. When the EL layer 15 is made of, e.g., a polymer organic material, an organic compound containing liquid containing a polymer organic material, which is formed on the display unit 7 by wet film formation, repels the surface of the liquid-repellent film 14. Hence, no film is formed on the liquid-repellent film 14. Instead, a film can selectively be formed in the opening portion 14a corresponding to each of the pixels  $P_{1,1}$  to  $P_{m,n}$ , i.e., on each pixel electrode 16. The organic compound containing liquid is a

liquid containing an organic compound as the material of the EL layer 15 or its precursor. This liquid may be a solution prepared by dissolving, as a solute, the organic compound as the material of the EL layer 15 or its precursor in a medium. Alternatively, the liquid may be a dispersion prepared by dispersing the organic compound as the material of the EL layer 15 or its precursor in a dispersion medium.

[0088] The light-emitting layer of the EL layer 15 is made of a light-emitting material. As the light-emitting material, a polymer-based material may be used. Examples of polymerbased materials are polycarbazole-, polyparaphenylene-, polyallylenevinylene-, polythiophene-, polyfluorene-, polysilane-, polyacetylene-, polyaniline-, polypyridine-, polypyridinevinylene-, and polypyrrole-based Examples of polymer materials are a polymer or copolymer of the monomer or oligomer of one of the above polymer materials (polymers), a polymer or copolymer of the derivative of the monomer or oligomer, or a polymer or copolymer prepared by polymerizing a monomer having an oxazole (oxandiazole, triazole, or diazole) or triphenylamine skeleton. The monomers of these polymers include monomers and precursor polymers which form the above-described compounds upon receiving heat, pressure, UV, or electron beam. A disconjugate unit which bonds the monomers may be introduced.

[0089] Detailed examples of the polymer materials are polyfluorene, polyvinylcarbazole, polydodecylthiophene, polyethylenedioxythiophene, sulfonate dispersoid polystyrene derivative, poly-9.9-dialkyl fluorene, poly(thienylene-9.9-dialkyl fluorene), poly(2.5-dialkyl paraphenylene-thienylene), (dialkyl: R=C1 to poly(2-methoxy-5-(2'-ethylpolyparaphenylenevinylene, hexyloxy)-paraphenylenevinylene), poly(2-methoxy-5-(2'ethyl-pentyloxy)-paraphenyleneviny lene), poly(2.5-dimethyl-paraphenylenevinylene), poly(2.5poly(2.5thienylenevinylene), dimethoxyparaphenylenevinylene), poly(1.4paraphenylenevinylenecyanovinylene).

[0090] The material is not limited to these polymer materials. The light-emitting layer may be formed by depositing a low molecular weight material. A low molecular weight material having a certain characteristic may be dissolved in a medium and applied. A low molecular weight material may be dispersed in a polymer as a dopant. Various kinds of polymers including known general-purpose polymers can be used as the polymer in which a low molecular weight material is polymer-dispersed.

[0091] The EL layer 15 is formed by wet film formation and has a two-layered structure in which a hole transport layer 15a made of PEDOT (polythiophene) as a conductive polymer and PSS (polystyrene sulfonate) as a dopant, and a light-emitting layer 15b made of a polyfluorene-based light-emitting material are formed in this order. When the EL layer 15 is formed by wet film formation, preferably, a lyophilic film having a characteristic (to be referred to as a "lyophilic effect" hereinafter) representing that the film surface wets well with a liquid at a contact angle of  $40^{\circ}$  or less is formed on the pixel electrode 16, and in this state, an organic compound containing liquid is applied to the lyophilic film.

[0092] The optical thickness (a layer thickness dxrefractive index n) of the transparent layer 19b of the optical

interference layer 19 is an integral multiple of ½ of the dominant wavelength (peak wavelength) of light emitted from the EL layer 15. Accordingly, the optical interference layer 19 has a resonant structure. More specifically, when light emitted from the EL layer 15 and, more particularly, light in the wavelength range near the dominant wavelength enters the optical interference layer 19, a light component having the dominant wavelength resonates by repeating reflection between the reflecting layer 19a and the halfreflecting layer 19c. Hence, the intensity of light emerging from the optical interference layer 19 increases. On the other hand, even when interference occurs while, of external light that enters the optical interference layer 19, a light component except the resonant dominant wavelength reflects between the reflecting layer 19a and the half-reflecting layer 19c, the phase does not coincide with the optical path length by the optical thickness of the transparent layer 19b. Since the light is gradually attenuated, it rarely emerges outside from the optical interference layer 19. The optical interference layer 19 can amplify the light emitted from the EL layer 15 and output light in a relatively wide wavelength range as light in a narrower wavelength range. Hence, the color purity of each color can be increased. In addition, glare caused by internal reflection of external light can be suppressed. For this reason, dark display or black display can be executed, and therefore, the contrast ratio can be increased. The optical thickness of the transparent layer 19b is preferably changed depending on the wavelength range of the color of emitted light of each pixel. When the pixels should emit light of R (red), G (green) having a shorter wavelength than red, and B (blue) having a shorter wavelength than green, the optical thicknesses are set to satisfy optical thickness of transparent layer 19b of pixel R>optical thickness of transparent layer 19b of pixel G>optical thickness of transparent layer 19b of pixel B.

[0093] The liquid-repellent film 14 (e.g., a fluoroplastic film or a reactive silicon film) having a characteristic (to be referred to as "liquid repellency" hereinafter) representing that the film surface repels a liquid and wets with it at a contact angle of 50° or more is formed on the optical interference layer 19 around each EL layer 15. When the liquid-repellent film 14 is formed into a mesh shape between the EL layers 15 when viewed from the upper side, a plurality of surrounded regions surrounded by the liquidrepellent film 14 are arrayed in a matrix, and the EL layers 15 are formed in the surrounded regions. As shown in FIG. 4, part of the liquid-repellent film 14 may overlap part of the edge of the pixel electrode 16. However, they need not always overlap. Especially, the EL layer 15 is formed as a very thin film. When the EL layer 15 is formed by wet film formation, and the organic compound containing liquid one-sidedly flows to adjacent pixels, some pixels obtain thin EL layers 15. This may cause short circuit between the pixel electrode 16 and the counter transparent electrode 13. However, the liquid-repellent film 14 which partitions the adjacent pixel electrodes 16 can prevent the organic compound containing liquid from flowing to adjacent pixels. In addition, when adjacent pixels are made of different materials which emit light of different colors, the liquid-repellent film 14 can prevent any decrease in purity of the color of emitted light of each pixel, which may be caused when the organic compound containing liquids of the adjacent pixels mix each other. The liquid-repellent film 14 may have a structure in which a material layer made of a resin or the like, which does not exhibit liquid repellency, is used as a dam that stores the organic compound containing liquid for each pixel, and a layer having liquid repellency may be formed on the exposed surface of the material layer. When the EL layer 15 is formed by epitaxial growth, the liquid-repellent film 14 need not be formed.

[0094] The counter transparent electrode 13 is formed as one common electrode of the organic EL elements E<sub>1.1</sub> to  $E_{mn}$  of all the pixels  $P_{1,1}$  to  $P_{m,n}$  The counter transparent electrode 13 is formed on the entire surface of the display unit 7 when viewed from the upper side and has a multilayered structure having an electron injection layer 13a and a transparent conductive layer 13b sequentially formed from the side of the EL layers 15. The electron injection layer 13a is so thin as to pass light and is made of a material having a relatively low work function (e.g., magnesium, calcium, lithium, barium, a single metal including a rare earth metal, or an alloy containing at least one of these single substances). The electron injection layer 13a has a thickness less than the visible light wavelength range and is 10 to 200 nm. The transparent conductive layer 13b is conductive and transparent to visible light. The transparent conductive layer 13b is made of, e.g., indium oxide, zinc oxide, or tin oxide, or a mixture containing at least one of them (e.g., indium tin oxide (ITO), indium zinc oxide, or cadmium tin oxide (CTO)). The resistivity of such a material is about  $100 \times 10^{-6}$  $\Omega$ cm to 1,000×10<sup>-6</sup>  $\Omega$ cm. The transparent conductive layer 13b is preferably thin to increase the light transmittance of the counter transparent electrode 13. The thickness of the transparent conductive layer 13b is 50 to 1,000 nm. As described above, the counter transparent electrode 13 passes at least part of the light emission wavelength range of the EL layer 15. The display apparatus 1 has a so-called top emission structure which outputs light from the EL layer 15 from the side of the counter transparent electrode 13.

[0095] The counter transparent electrode 13 may be divided into two or more parts. The counter transparent electrode 13 may include a plurality of stripe-shaped electrodes which are commonly connected to pixels adjacent in the column direction. Alternatively, the counter transparent electrode 13 may include a plurality of stripe-shaped electrodes which are commonly connected to pixels adjacent in the row direction. A plurality of insulating protective layers 41 are formed on the counter transparent electrode 13 almost in correspondence with the regions where the EL layers 15 are formed. The plurality of insulating protective layers 41 are arrayed in a matrix independently for each pixel when viewed from the upper side, like the EL layers 15. The insulating protective layer 41 is transparent and is made of, e.g., an inorganic silicide such as silicon oxide (SiO<sub>2</sub>) or silicon nitride (SiN) or an organic resin such as polyimide.

[0096] A conductive auxiliary electrode layer 42 is formed in each non-display region located between edge portions 41a of the insulating protective layer 41 in the display unit 7. Between the insulating protective layers 41, the auxiliary electrode layer 42 is in direct contact with the transparent conductive layer 13b. The auxiliary electrode layer 42 is formed into a mesh shape while substantially overlapping the entire region between the plurality of pixel electrodes 16 when viewed from the upper side. The insulating protective layer 41, EL layer 15, pixel electrode 16, and optical interference layer 19 are arranged in the region in each opening portion 42a of the auxiliary electrode layer 42. An

edge portion 42b of the auxiliary electrode layer 42 can be formed either inside or outside the edge portion of the counter transparent electrode 13. To reduce the sheet resistance, the occupation area of the auxiliary electrode layer 42 is preferably close to the entire non-display region in the display unit 7 as much as possible. The edge portion 41a of the insulating protective layer 41 extends outside the opening portion 42a of the auxiliary electrode layer 42. Hence, in patterning the auxiliary electrode layer 42 by etching, the insulating protective layer 41 can protect the transparent conductive layer 13b from the etchant. The auxiliary electrode layer 42 is located to overlap the first transistor 8, second transistor 9, and third transistor 10 when viewed from the upper side.

[0097] The auxiliary electrode layer 42 functions as an electrode integrated with the counter transparent electrode 13 and decreases the sheet resistance as compared to the single counter transparent electrode 13. The auxiliary electrode layer 42 is made of a material which has a lower resistivity than the material of the transparent conductive layer 13b and is hardly oxidized. From this viewpoint, copper (resistivity:  $1.67 \times 10^{-6} \Omega$ cm), silver (resistivity:  $1.59 \times 10^{-6} \ \Omega$ cm), gold (resistivity:  $2.35 \times 10^{-6} \ \Omega$ cm), platinum (resistivity:  $10.6 \times 10^{-6} \Omega$ cm), aluminum (resistivity:  $2.66\times10^{-6} \Omega$ cm), or chromium (resistivity:  $12.9\times10^{-6} \Omega$ cm), or an alloy containing at least one of them is preferably used. In addition, the auxiliary electrode layer 42 is located to overlap the positions of the selection scan lines  $X_1, X_2, \ldots$ ,  $X_m$ , current lines  $Y_1,Y_2,\ldots,Y_n$ , and voltage source scan lines  $Z_1,Z_2,\ldots,Z_m$  connected to the first transistors  ${\bf 8}$ , second transistors 9, and third transistors 10 when viewed from the upper side. When a light-shielding material having a low reflectance is used, the auxiliary electrode layer 42 can be used as a light-shielding film (black mask) between the pixels. The thickness of the auxiliary electrode layer 42 is preferably about 10 to 1,000 nm and, to obtain a larger light-shielding effect, preferably 50 nm or more. If the selection scan lines  $X_1,\,X_2,\,\ldots,\,X_m$ , current lines  $Y_1,\,Y_2,$  $\ldots$  ,  $\boldsymbol{Y}_n$  , or voltage source scan lines  $\boldsymbol{Z}_1,\,\boldsymbol{Z}_2,\,\ldots$  ,  $\boldsymbol{Z}_m$  are wiring lines made of a conductive material having a reflectance, and the optical interference layer 19 does not overlap the wiring lines made of the conductive material having a reflectance, or if at least the selection scan lines  $X_1, X_2, \dots$ . ,  $X_m$ , current lines  $Y_1, Y_2, \dots, Y_n$ , or voltage source scan lines  $Z_1, Z_2, \ldots, Z_m$  are wiring lines made of a conductive material having a reflectance, and the display apparatus 1 has no optical interference layer 19, the auxiliary electrode layer 42 can suppress reflection by external light in the wiring lines made of the conductive material having a reflectance. Hence, the visibility can be increased. In this case, more specifically, the auxiliary electrode layer 42 preferably contains at least one of chromium, chromium oxide, a chromium alloy, nickel-tantalum alloy, nickelcopper alloy, and any other nickel alloy. The luster of the auxiliary electrode layer 42 may be eliminated to obtain a lower reflectance by forming a very small three-dimensional pattern on its surface. When the transparent conductive layer 13b is not formed, the auxiliary electrode layer 42 may come into direct contact with a part of the electron injection layer 13a between the insulating protective layers 41. When the electron injection layer 13a is not formed, the auxiliary electrode layer 42 may come into direct contact with the counter transparent electrode 13 including only the transparent conductive layer 13b between the insulating protective layers 41. As described above, the auxiliary electrode layer 42 is formed around the pixel  $P_{i,j}$ . Hence, the auxiliary electrode layer 42 can be deposited thick enough to be opaque. For this reason, the sheet resistance can greatly be reduced.

[0098] Since the auxiliary electrode layer 42 is made of a material having a lower resistivity than the transparent conductive layer 13b, the sheet resistance of the electrode on the upper side of the EL layer 15 can be reduced. In addition, the auxiliary electrode layer 42 does not overlap the portion of the transparent conductive layer 13b, which is located in the display region. For this reason, light from the EL layer 15 can pass the portion of the transparent conductive layer 13b, which is located in the display region, and be output without being shielded by the auxiliary electrode layer 42.

[0099] If there is no auxiliary electrode layer 42, the voltage in the counter transparent electrode 13 is attenuated in a pixel far apart from the wiring source, which outputs the reference potential  $V_{\rm SS}$  to the counter transparent electrode 13, as compared to a pixel close to the wiring source because the sheet resistance of the counter transparent electrode 13 is high. This makes the current density nonuniform and generates a variation in light emission luminance in the plane. However, when the auxiliary electrode layer 42 is used, the sheet resistance of the electrode of each organic EL element can be reduced. Hence, the density of current flowing to the counter transparent electrodes 13 of the pixels can be made constant without reducing the transmittance, and uniform light emission can be caused in the display unit 7

[0100] A light-shielding film 44 is formed on the auxiliary electrode layer 42, i.e., in a non-display region. The lightshielding film 44 is formed in a matrix when viewed from the upper side, like the auxiliary electrode layer 42, and overlaps the auxiliary electrode layer 42. The light-shielding film 44 itself need not be conductive but has a light-shielding effect and low reflectance. The light-shielding film 44 is located to overlap the auxiliary electrode layer 42 which overlaps the first transistors 8, second transistors 9, third transistors 10, selection scan lines  $X_1, X_2, \ldots, X_m$ , current lines  $Y_1, Y_2, \ldots, Y_n$ , and voltage source scan lines  $Z_1, Z_2$ , ...,  $Z_{\rm m}$  when viewed from the upper side. Hence, the structure of the light-shielding film 44 can suppress light reflection by these components and make reflected light almost invisible. The light-shielding film 44 can be made of a material prepared by, e.g., dispersing a black pigment having a light-shielding effect and low reflectance, such as carbon black, in a matrix (binder) such as a resin. Alternatively, the light-shielding film 44 may be made of a resin having a light-shielding effect and low reflectance or a metal such as chromium oxide. In this case, the auxiliary electrode layer 42 itself need not have the light-shielding effect and low reflectance, or the auxiliary electrode layer 42 itself may have the light-shielding effect and low reflectance

[0101] The insulating protective layers 41 and light-shielding film 44 are covered with a sealing film 43. The sealing film 43 is formed over the entire upper surface-of the substrate 12. The sealing film 43 cancels steps generated between the insulating protective layers 41 and the auxiliary electrode layer 42. The sealing film 43 has an almost flat upper surface. The sealing film 43 has a characteristic that passes light and is made of a transparent resin (e.g., methacrylic resin, acrylic resin, or epoxy resin).

[0102] The pixel electrodes 16 do not overlap the selection scan lines  $X_1$  to  $X_m$ , current lines  $Y_1$  to  $Y_n$ , and voltage source scan lines  $Z_1$  to  $Z_m$  when viewed from the upper side to suppress any delay of the current flowing to the wiring lines caused by the parasitic capacitance between the pixel electrodes 16 and the wiring lines. However, if the insulating planarization film 18 is so thick as to sufficiently relax the parasitic capacitance, the pixel electrodes 16 may overlap the wiring lines. Accordingly, the EL layers 15 on the pixel electrodes 16 can also be made large. Hence, the display area can be increased, or the display area ratio in the display unit 7 can be made high.

[0103] The upper portion of the sealing film 43 may hermetically be sealed by a glass substrate, as needed.

[0104] The pixel driving circuits  $D_{1,1}$  to  $D_{m,n}$  of the display apparatus 1 are of a current gray level type which displays multiple gray levels by controlling the value of the signal current flowing to one of the third transistors 10, as will be described later. However, the present invention is not limited to this. The pixel driving circuits may be of a voltage gray level type which displays multiple gray levels by controlling the voltage value of the signal voltage applied to the pixel driving circuits  $D_{1,1}$  to  $D_{m,n}$ .

[0105] A method of manufacturing the display apparatus 1 will be described next.

#### (1) Array Substrate Manufacturing Step

[0106] As shown in FIGS. 7A and 7B, the first transistor 8, second transistor 9, and third transistor 10 of each pixel are formed on the display unit 7 of the flat substrate 12. In addition, the selection scan lines  $X_1, X_2, \ldots, X_m$ , current lines  $Y_1, Y_2, \ldots, Y_n$ , and voltage source scan lines  $Z_1, Z_2, \ldots, Z_m$  are formed. After that, the transistors 8 to 10 and the wiring lines  $X_1$  to  $X_m$ ,  $Y_1$  to  $Y_n$ , and  $Z_1$  to  $Z_m$  are selectively covered with the protective insulating film 29 made of silicon nitride or silicon oxide. The insulating planarization film 18 made of a resin such as polyimide is deposited on the protective insulating film 29 in correspondence with the entire region of the display unit 7. Then, the reflecting layer 19a, transparent layer 19b, and half-reflecting layer 19c are sequentially formed to form the optical interference layer 19.

#### (2) Opening Portion Formation Step

[0107] As shown in FIGS. 8A and 8B, the contact hole 49 which communicates with the source electrode layer 28 of the third transistor 10 of each pixel are formed in the optical interference layer 19, insulating planarization film 18, and protective insulating film 29 by photolithography. An opening portion 18a of the insulating planarization film 18 forms part of the contact hole 49. When the height of the insulating planarization film 18 is more than the thickness of the pixel electrode 16, the opening portion 18a may be filled with a conductive material before formation of the pixel electrodes 16.

#### (3) Pixel Electrode Array Formation Step

[0108] As shown in FIGS. 9A and 9B, a transparent conductive film (e.g., an ITO film) is formed on the entire surface of the optical interference layer 19 by epitaxial growth. A resist is formed in a matrix on the conductive film

by the photoresist process. The conductive film is processed by etching or the like by using the resist as a mask. After that, the resist is removed. The remaining conductive film becomes the pixel electrode 16 which is electrically connected to the source electrode layer 28 of the third transistor 10 through the contact holes 49. The plurality of pixel electrodes 16 can be patterned in a matrix. Each of the plurality of pixel electrodes 16 is arranged in a corresponding display region surrounded by the first transistor 8, second transistor 9, and third transistor 10 of each pixel. The pixel electrodes 16 are also electrically isolated from each other. The edge portion 16a has been formed along the first transistor 8, second transistor 9, and third transistor 10. The pixel electrodes 16 overlap the optical interference layer 19 when viewed from the upper side. If an etchant for the transparent conductive film may erode the optical interference layer 19, an insulating layer having a high etching resistance may be inserted between the optical interference layer 19 and the pixel electrodes 16.

#### (4) Liquid-Repellent Film Formation Step

[0109] As shown in FIGS. 10A and 10B, the liquid-repellent film 14 having the opening portions 14a to which the central portions of the pixel electrodes 16 are exposed is formed into a mesh shape on the display unit 7. At this time, the edges which define the opening portion 14a of the liquid-repellent film 14 cover the edge portions 16a of the pixel electrodes 16. The liquid-repellent film 14 may be formed by photolithography and then etching. The liquid-repellent film 14 may be a fluoroplastic film such as a silazane compound which has Si—N—Si bonds and a functional group containing fluorine in which a functional group containing fluorine is bonded to N or/and Si, or a reactive silicon film.

[0110] The EL layers 15 may be formed in the following way. The liquid-repellent film 14 is formed on the entire surface of the display unit 7. A photocatalyst which generates an active species that promotes chemical reaction to eliminate the liquid repellency upon receiving light in a predetermined wavelength range is placed on the liquidrepellent film 14 on the upper surface of each pixel electrode 16. The light in the predetermined wavelength range is caused to become incident from the upper surface of the photocatalyst to impart a lyophilic effect to the liquidrepellent film 14 on the pixel electrode 16 where the EL layer 15 should be formed. The EL layer 15 is formed on the liquid-repellent film 14 by a method to be described later. More specifically, a liquid containing silazane compound is applied thin to the entire surface of the display unit 7. After the silazane compound is converted into a polymer, the liquid is dried, and a photocatalyst such as titanium oxide is placed on the pixel electrodes 16. The photocatalyst is selectively irradiated with UV rays to eliminate fluorine or a functional group containing fluorine from the silazanebased polymer on the pixel electrodes 16 to eliminate the liquid repellency of the liquid-repellent film 14. The liquid repellency of the liquid-repellent film 14 located between the pixel electrodes 16 may be maintained without irradiating it with UV rays. The liquid-repellent film 14 having no liquid repellency is an insulating film. However, the liquidrepellent film 14 formed on the pixel electrode 16 does not so greatly impede injection of carriers such as holes or electrons because the liquid-repellent film 14 is very thin. The liquid-repellent film 14 may be formed as a base which is made of polyimide and has the opening portion **14***a* as a sidewall, and a liquid-repellent material such as a fluorine-based material may be applied thin to the surface of the base.

#### (5) EL Layer Formation Step

[0111] As shown in FIGS. 11A and 11B, the EL layers 15 are formed on the pixel electrodes 16 exposed by the opening portions 14a of the liquid-repellent film 14. In patterning the EL layers 15, they may selectively be deposited by using a droplet ejection nozzle (inkjet nozzle) which ejects a liquid containing the material of the EL layers 15. More specifically, the nozzle is made to oppose the substrate 12 placed on a stage. The nozzle is moved parallel to the substrate 12, and when the nozzle is located on a surrounded region, it ejects the organic compound containing liquid. Accordingly, the EL layers 15 can be formed to overlap the pixel electrodes 16 when viewed from the upper side.

[0112] When the EL layer 15 includes the hole transport layer 15a and light-emitting layer 15b, a nozzle for the hole transport layer first ejects a liquid containing the material of the hole transport layer 15a as a droplet to each region surrounded by the opening portion 14a of the liquid-repellent film 14. After the liquid dries, and the hole transport layer 15a is formed, a nozzle for the light-emitting layer 15b of narrow sense ejects a liquid containing the material of the light-emitting layer 15b as a droplet to each region surrounded by the opening portion 14a of the liquid-repellent film 14. The liquid dries, and the light-emitting layer 15b is formed. Even when the droplet containing the material of the hole transport layer 15a or light-emitting layer 15b drops to the edge of the liquid-repellent film 14, the droplet is repelled by the liquid-repellent film 14 and falls into the opening portion (pixel electrode 16) surrounded by the liquid-repellent film 14. If the liquid-repellent film 14 can sufficiently repel the droplet, the EL layers 15 may be formed by printing. At this time, the liquid-repellent film 14 partitions the liquid containing the material of the EL layers 15 between adjacent pixels even when the accuracy of the printing technique is not so high as photolithography. Hence, pixels with a fine pitch can be formed.

[0113] A metal mask having a mesh shape may be formed over the substrate 12 while exposing the pixel electrodes 16. The EL layers 15 may be formed in a matrix by executing epitaxial growth in this state. If the hole transport layers 15a of the pixels can be made of the same material regardless of the colors of light emitted by the EL layers 15, the display unit 7 may wholly be dipped in a liquid containing the material of the hole transport layer 15a. Accordingly, the EL layers 15 can selectively be formed on the pixel electrodes 16 by the patterned liquid-repellent film 14. Instead of forming the liquid-repellent film 14, the hole transport layer 15a may be formed as a continuous layers across the pixels by wholly dipping the display unit 7 in the liquid containing the material of the hole transport layer 15a.

#### (6) Counter Transparent Electrode Formation Step

[0114] As shown in FIGS. 12A and 12B, a layer made of magnesium, calcium, lithium, barium, a single metal including a rare earth metal, or an alloy containing at least one of these single substances is formed over the entire surface of the display unit 7 (on the layers 14 and 15) to a thickness of 10 to 200 nm by sputtering or deposition in an inert gas

atmosphere such as argon or in a reduced pressure atmosphere at 1 Torr or less, thereby forming the electron injection layer 13a. Subsequently, a material selected from indium tin oxide (ITO), indium zinc oxide, and cadmium tin oxide (CTO) is formed on the entire surface of the formed layer 13a to a thickness of 50 to 200 nm by sputtering or deposition such as CVD, thereby forming the transparent conductive layer 13b on the electron injection layer 13a.

#### (7) Insulating Protective Layer Array Formation Step

[0115] As shown in FIGS. 13A and 13B, epitaxial growth, photoresist process, etching, and resist removal are sequentially executed to pattern the plurality of transparent insulating protective layers 41 in a matrix. The insulating protective layers 41 are formed to overlap the EL layers 15 when viewed from the upper side. The insulating protective layer 41 has a high transmittance to visible light and is made of an inorganic silicide such as silicon oxide or silicon nitride or an organic resin such as polyimide. When the insulating protective layers 41 are made of an organic resin, they may directly be patterned in a matrix by using a droplet ejection technique (inkjet technique) instead of sequentially executing epitaxial growth, photoresist process, etching, and resist removal.

#### (8) Auxiliary Electrode Layer Formation Step

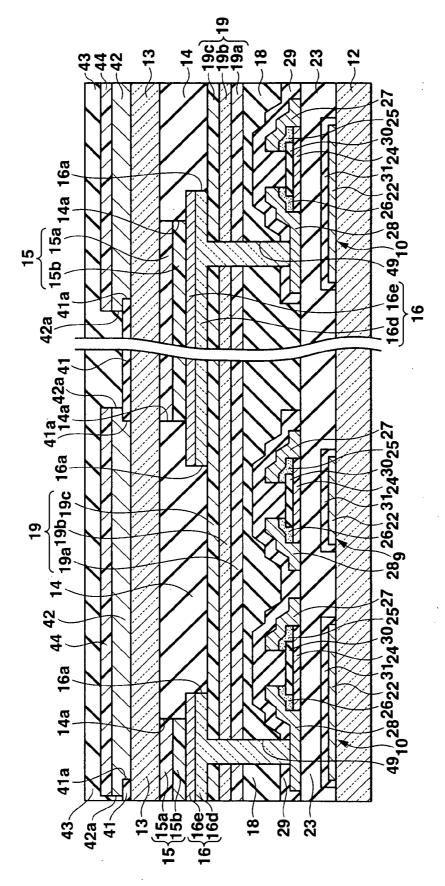

[0116] As shown in FIGS. 14A and 14B, a conductive film having a light-shielding effect, which is made of e.g., copper, silver, gold, platinum, aluminum, chromium, and an alloy containing at least one of them, is formed on the counter transparent electrode 13 by epitaxial growth such as sputtering. In addition, a light-shielding resin prepared by dispersing carbon black in a resin or a light-shielding metal such as chromium oxide is formed on the formed conductive film and then patterned at once by etching by photolithography to form the auxiliary electrode layer 42 and the light-shielding film 44 on it. The auxiliary electrode layer 42 preferably has a resistivity of  $50.0 \times 10^{-6} \Omega$ cm or less and a thickness of about 10 to 1,000 nm. The insulating protective layer 41, EL layer 15, pixel electrode 16, and optical interference layer 19 are arranged in the region in each opening portion 42a of the auxiliary electrode layer 42. The edge portion 41a of the insulating protective layer 41 extends outside the opening portion  $\hat{42}a$  of the auxiliary electrode layer 42. Hence, in patterning the auxiliary electrode layer 42 by etching, the insulating protective layer 41 can protect the transparent conductive layer 13b from the etchant. The electron injection layer 13a which is relatively easily oxidized is also covered with the insulating protective layer 41 and transparent conductive layer 13b. Hence, even when one of the insulating protective layer 41 and transparent conductive layer 13b has any pinhole, the other layer protects the electron injection layer 13a so that it can be prevented from being oxidized by the etchant. In addition, the auxiliary electrode layer 42 and light-shielding film 44 have a shape that overlaps the first transistors 8, second transistors  $\hat{\mathbf{9}}$ , third transistors  $\mathbf{10}$ , selection scan lines  $X_1, X_2$ ,  $\ldots$ ,  $X_m$ , current lines  $Y_1, Y_2, \ldots, Y_n$ , and voltage source scan lines  $Z_1, Z_2, \ldots, Z_m$  when viewed from the upper side. When the light-shielding film 44 is to be formed by oxidizing the conductive material (e.g., chromium) of the auxiliary electrode layer 42, the light-shielding film 44 may be formed by forming the auxiliary electrode layer 42 and oxidizing its upper surface portion. The thickness of the conductive material formed at this time includes in advance the portion to be oxidized for the light-shielding film 44. When the conductive film is a chromium film, wet etching may be executed by using, as an etchant, a solution mixture containing ceric ammonium nitrate and perchloric acid.

#### (9) Step of Forming Sealing Film

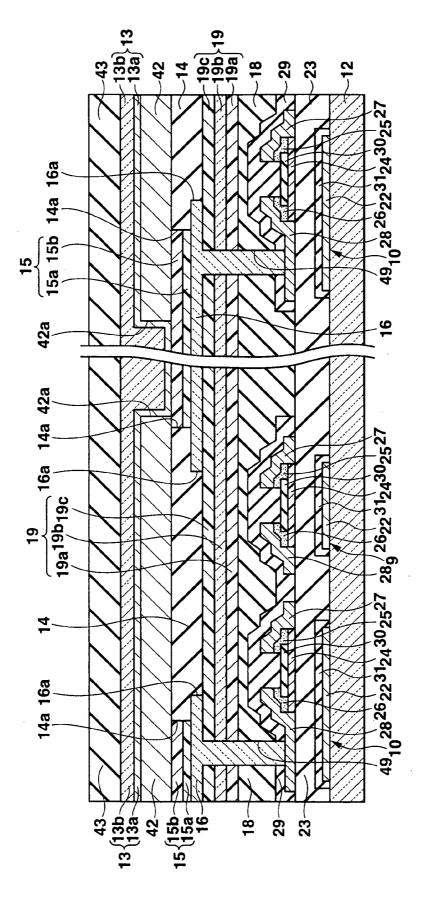

[0117] As shown in FIGS. 15A and 15B, the sealing film 43 prepared by inserting thin metal films and inorganic compound layers between a plurality of resin films is formed over the entire display unit 7. At this time, the sealing film 43 preferably covers all the components in the display unit 7 as much as possible, except components extending outside the region of the display unit 7, such as the terminals of the selection scan lines  $X_1$  to  $X_m$ , current lines  $Y_1$  to  $Y_n$ , and voltage source scan lines  $Z_1$  to  $Z_m$  and the terminals of the counter transparent electrode 13 of the organic EL elements  $E_{1,1}$  to  $E_{m,n}$ . To smoothen the surface of the sealing film 43 to efficiently output light from the EL layers 15, the surface of the sealing film 43 may be subjected to chemical polishing, mechanical polishing, or chemical mechanical polishing. In addition, a counter substrate opposing the substrate 12 may be arranged above the sealing film 43 to arrange the display unit 7 between the substrates.

[0118] In the display apparatus manufactured in the above way, the selection scan driver 3, voltage source driver 4, and data driver 5 control the pixel driving circuits  $D_{1,1}$  to  $D_{m,n}$  of the pixels  $P_{1,1}$  to  $P_{m,n}$  through the selection scan lines  $X_1$  to  $X_m$ , current lines  $Y_1$  to  $Y_n$ , and voltage source scan lines  $Z_1$  to  $Z_m$  to cause the organic EL elements  $E_{1,1}$  to  $E_{m,n}$  to appropriately emit light so that the light emerges outside from the side of the counter transparent electrode 13. Hence, the display surface is formed on the side of the counter transparent electrode 13. A user who opposes the side of the counter transparent electrode 13 can see the displayed contents.

[0119] As described above, in this embodiment, the auxiliary electrode layer 42 having a mesh shape is formed directly on the counter transparent electrode 13 while overlapping the non-display regions between the plurality of pixel electrodes 16. For this reason, even when the counter transparent electrode 13 is made of, e.g., a metal oxide material having a relatively high resistivity, the sheet resistance of the entire electrode can be reduced to make a current easily flow while the decrease of the aperture ratio is minimized. In addition, since the low resistive auxiliary electrode layer 42 arranged on the entire region of the counter transparent electrode 13, the applied voltage on a side of the counter transparent electrode 13 can be uniformed in the plane. Even if the same potential is applied to all the pixel electrodes 16, the value of the flowing current becomes uniform. All the EL layers 15 can emit light almost at the same intensity, and the light emission intensity in the plane can be uniformed.

[0120] Furthermore, since the auxiliary electrode layer 42 with a low resistance sufficiently reduces the sheet resistance of the entire electrode, the counter transparent electrode 13 can be made thinner to suppress the degree of attenuation of light emitted from the EL layers 15 in passing through the counter transparent electrode 13. As described above, a